Team: System Solutions

# Basic Data Acquisition Test

Data Acquisition Test 1

Alexis Wilson 2-9-2020

## TABLE OF CONTENTS

| TABLE OF CONTENTS   | 1 |

|---------------------|---|

| REVISION HISTORY    | 2 |

| TEST PROCEDURE      | 3 |

| PURPOSE OF TEST     | 3 |

| REQUIREMENTS        | 3 |

| TEST IMPLEMENTATION |   |

| Setup               | 3 |

| Procedure           | 5 |

| Results             | 5 |

| CONCLUSION          | 6 |

# **Revision History**

| Name          | Date       | Revision Made | Version Number |

|---------------|------------|---------------|----------------|

| Alexis Wilson | 02/09/2020 | Creation of   | 1.0            |

|               |            | Document      |                |

|               |            |               |                |

|               |            |               |                |

|               |            |               |                |

#### **Purpose of Test:**

The purpose of this test is to verify that it is possible to receive a signal/data from and external source and view it on the FPGA. This is the first test for the Data Acquisition tests and should be performed before the more advanced tests. This test will prove that we will be able to receive signals from the Pound-Drever-Hall loop.

#### **Requirements:**

To perform this test, one will need a STEMLab 125-14 Field Programmable Gate Array (FPGA) and with a power cable and an Ethernet cable. One will also need a switch/hub, an Ethernet cable, and a laptop/computer. No internet or outside source will be required to send and receive signals; however, one will need a Function Generator to send a signal into the FPGA. Knowledge of signals and external noise on a system may help with interpreting any irregularities in the input signal coming from the output of the other board.

NOTE: This test can be run with more than 1 board, it will just require more repetitions at certain steps.

CAUTION: Before touching the STEMLab 125-14 board, make sure to ground oneself by touching metal or wearing an ESD strap so that no electric discharge can cause harm to the components on the board.

### **Test Implementation:**

#### Setup:

- 1. Take the STEMLab 125-14 board out of the box and plug in the FPGA to an outlet.

- a. The power plug in is on the left side of the board far left of the ethernet cable.

- 2. Take an ethernet cable and plug it back into ethernet slot on the FPGA.

- 3. Take the other end of the ethernet cable and plug it into a LAN slot of the network switch/hub.

- 4. Take the second Ethernet cable and plug it into the Ethernet port of the computer/laptop. Shown in Figure 1 below:

Figure 1: Set Up Between FPGA and Switch/Hub

- 5. Once the board is on and link light is coming from the switch for both ethernet connections, use an internet browser to connect to the board through Ethernet

- a. Type rp-xxxxxx.local/ and press enter

- b. The resulting screen should pop up if connection is true shown in Figure 2 below:

Figure 2: Red Pitaya Interface Page

- 6. Connect the function generator up to the Red Pitaya Fast Analog Input IN1 using a BNC-SMA connector.

- a. BNC connection goes into Function Generator

- b. SMA connector connects into IN1

- 7. On the Red Pitaya, click on the Oscilloscope and Function Generator Button

- 8. Turn on the Function Generator

- 9. Once the Function generator is on and the Oscilloscope is up on the Red Pitaya, Setup is complete

#### Procedure:

- 1. On the Function Generator, generator a 1000 Hz Sine wave signal

- 2. On the Red Pitaya Oscilloscope, Click on Signal IN1 Settings

- a. Click Show

- b. Change the Volts from the 1 Volt range to the 10 Volt Range

- c. Change the Operator to frequency

- d. Press done

- 3. Go back into the Signal IN1 settings

- a. Click Show

- b. Change the Volts from the 1 Volt range to the 10 Volt Range

- c. Change the Operator to P2P

- d. Press done

- 4. Back out of the Signal IN1 and click run on the top right-hand side of the screen

#### Results:

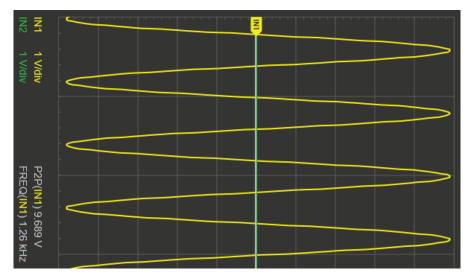

- 1. At step four of the procedure, one should see a signal:

- a. With a frequency output of 1000 Hz

- b. Should have Peak to Peak of nearly 10V

The picture in Figure 3 below shows an expected output with the input Frequency being around 1.25 kHz with a Peak-to-peak voltage range of 10V

Figure 3: Results Example of 1.25 kHz at 10V range

## **Conclusion:**

The purpose of this test is to verify that it is possible to receive a signal/data from and external source and view it on the FPGA. This is the first test for the Data Acquisition tests and should be performed before the more advanced tests. Without this test, we would have to check for the FPGA's ability to receive external data from a non-Red Pitaya source before it would be apparent that the data being received from a system is accurate.