#### INTO THE WIND

Keegan Miley-Hunter (Manufacture Lead), Mason Taylor (Software Lead), Mason Ulrich (Hardware Lead) SUPERVISOR/CLIENT:

> Joe Law INSTRUCTOR: Herb Hess

#### Objective

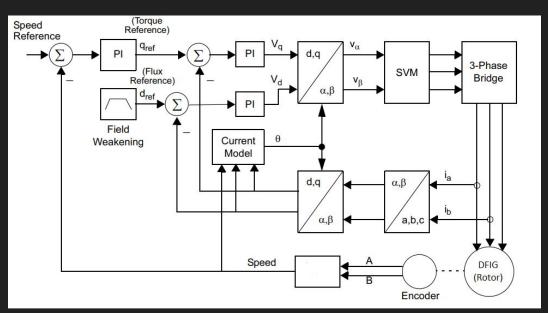

Design and implement a rotor side converter to monitor a DFIG's Torque, Current and Voltage output in order to command an input waveform that will stabilize the DFIG with the grid at 60Hz.

#### Value Proposition

Completion of this project will assist in the advancement of wind energy systems by allowing further research to be conducted on subsynchronous resonance of a doubly fed induction generator (DFIG).

## Background

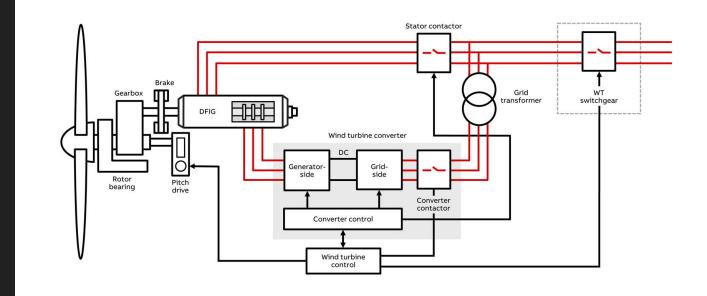

- Use in Type III wind energy systems

- Need for research of advanced topics

- Desire for lab based test system

#### Requirements

- Modular

- Robust

# Conceptual Development

- Learn

- Design verification

- Hardware selection

- Hardware module testing

- Project code

- Circuit/Stand Build

|                                                    |       |         | 2020  |           |                                         |        |        |        |          |        |        |         |        |         |                      |        |        |        |       |                                         |       |         |       |       |       |      |     |         |

|----------------------------------------------------|-------|---------|-------|-----------|-----------------------------------------|--------|--------|--------|----------|--------|--------|---------|--------|---------|----------------------|--------|--------|--------|-------|-----------------------------------------|-------|---------|-------|-------|-------|------|-----|---------|

|                                                    |       |         | Jan   | 2010 Card |                                         |        | March  |        | April    |        | May    |         |        | June    |                      | July   |        | August |       | Septemb                                 | ber   | October | ber   | N     | loven | nber | D   | ecember |

|                                                    |       |         | 12 19 | 26 2      | 9 16 2                                  | 3 1 8  | 3 15 2 | 22 29  | 5 12 1   | 9 26   | 3 10 1 | 17 24 3 | 1 7    | 14 21 2 | . <mark>8</mark> 5 : | 12 19  | 26 2   | 9 16   | 23 30 | 6 13 20                                 | 27    | 4 11    | 18 25 | 1     | 8 15  | 22 2 | 9 6 | 13 20 2 |

| Tasks/Outcomes                                     | Start | End     |       |           |                                         |        |        |        |          |        |        |         |        |         |                      |        |        |        |       |                                         |       |         |       |       |       |      |     |         |

| Name                                               | Date  | Date    |       |           |                                         |        |        |        |          |        |        |         |        |         |                      |        |        |        |       |                                         |       |         |       |       |       |      |     |         |

| Learn                                              | 1/30  | 5       |       | 1111      | /////////////////////////////////////// | 1      |        |        |          |        |        |         |        |         |                      |        |        |        |       |                                         |       |         |       |       |       |      |     |         |

| b Design Verification (simulations)                | 3/1   | 9/20    |       |           |                                         |        |        | ////// | //////// | /////  |        |         | ////// |         | //////               |        | ////// | ////// |       | /////////////////////////////////////// | 1     |         |       |       |       |      |     |         |

| c Hardware Selection (examine and compare options) | 2/13  | 9/28    |       |           |                                         | ////// | ////// | ////// | //////// | ////// |        |         | ////// |         | //////               | ////// | ////// |        |       | /////////////////////////////////////// |       |         |       |       |       |      |     |         |

| d Hardware module testing (subsystem testing)      | 6/8   | 11/18   |       |           |                                         |        |        |        |          |        |        |         | 111    |         |                      |        |        |        |       |                                         | 11111 | 11111   | 11111 | 1111  | 11111 |      |     |         |

| e Project Code                                     | 9/15  | 12/11   |       |           |                                         |        |        |        |          |        |        |         | 1000   |         |                      |        |        |        |       |                                         |       |         | ///// |       |       |      | 1   |         |

| f Circuit/Stand Build                              | 9/13  | 1/20/20 |       |           |                                         |        |        |        |          |        |        |         |        |         |                      |        |        |        |       | HIII                                    | HIII  |         | 1111  | IIIII |       |      |     |         |

|                                                    |       |         |       |           |                                         |        |        |        |          |        |        |         |        |         |                      |        |        |        |       |                                         |       |         |       |       |       |      |     |         |

#### EVALUATION

Learning

Power Electronics

Controls Flow

Design Verification

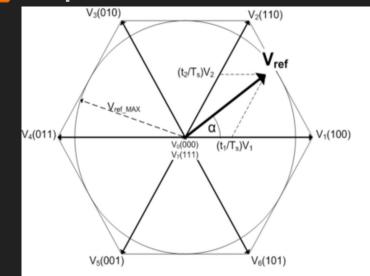

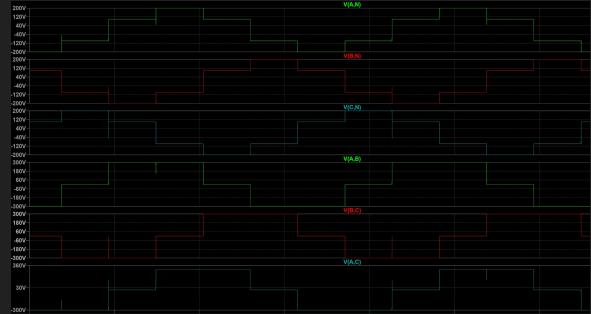

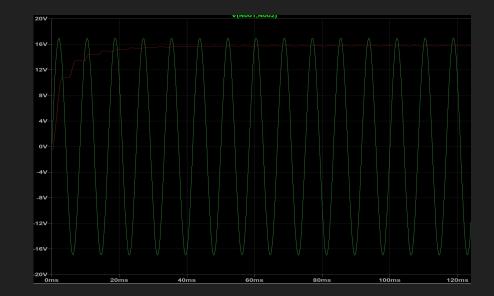

Space Vector Simulations

Spice Simulations

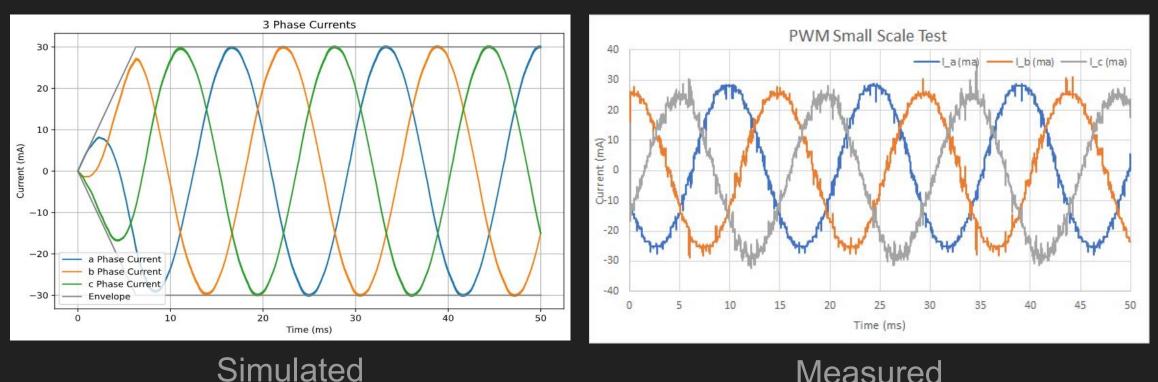

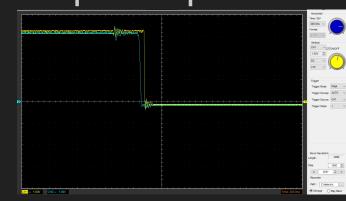

#### **Space Vector Modulation Testing**

- Python simulation of Space Vector Modulation

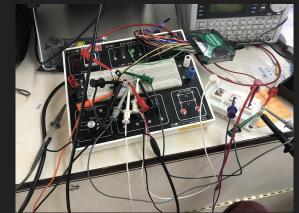

- **PWM Small Scale Testing**

- Uses Gate Drivers, Power MOSFETs, and a 3-phase Y circuit with R-L load

Measured

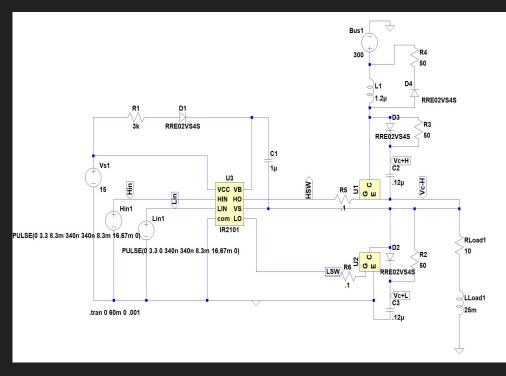

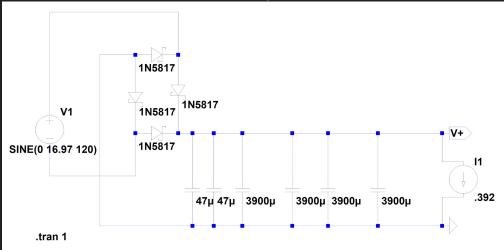

### Spice Simulations

Single leg and H-Bridge

ldeal 6-step

HV Power Supply

## EVALUATION

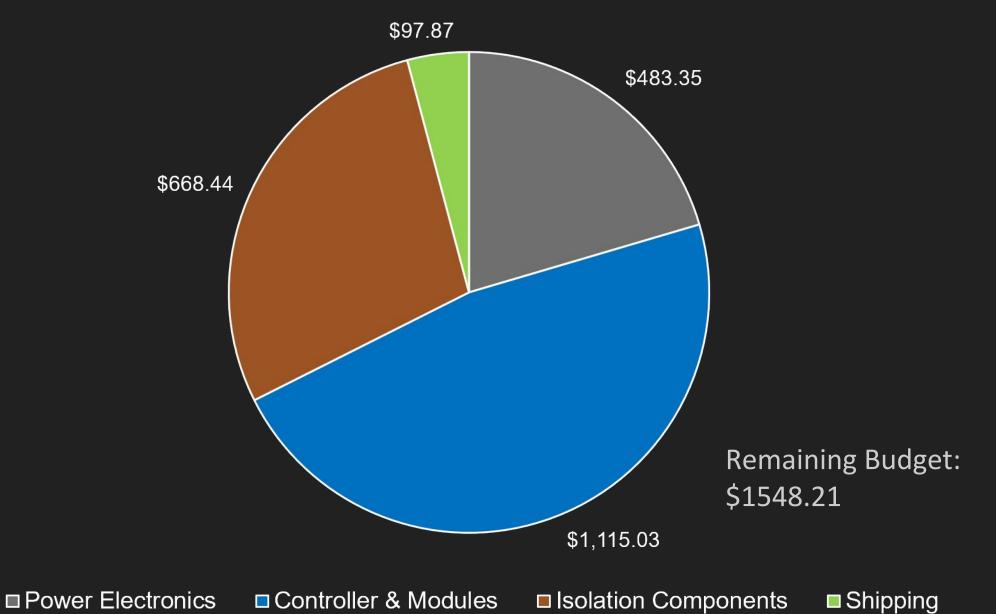

Hardware Selection

- Identify components needed

- Define component parameters

- Verify specifications and compare options

Hardware Module Testing

- Test Plan Development

- Assemble components individually

- Test in isolation

- Subsystem Tests

#### EVALUATION

Project Code

- Test subsystems

- Basic control code

Integrate and finalize

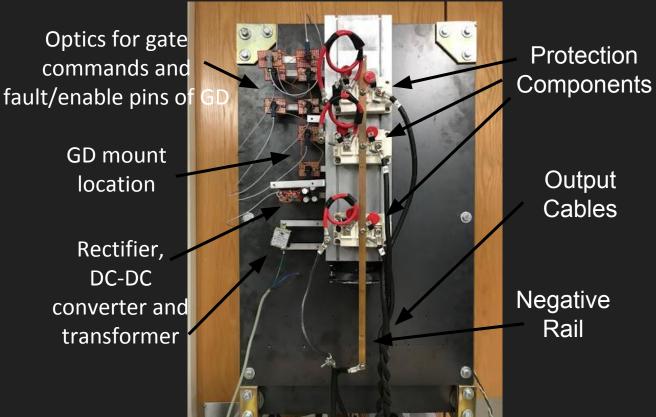

#### **Circuit/Stand Build**

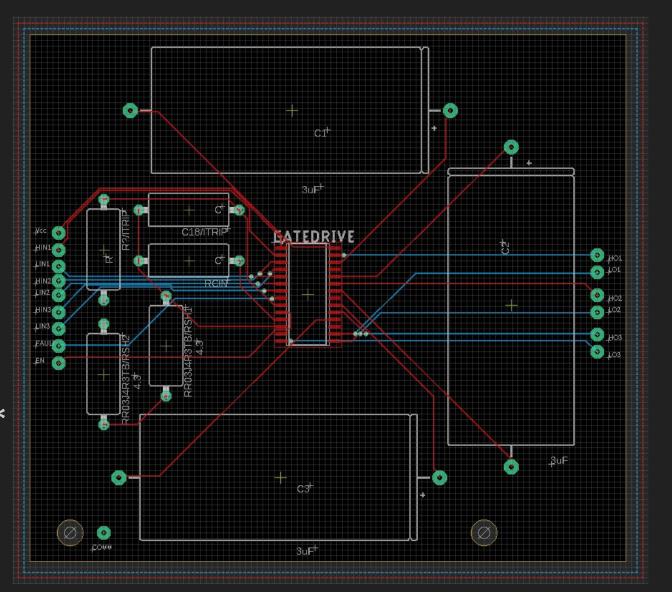

Manufacturing/soldering PCBs

Mounting and system connection

#### Key Attributes to Design

Modular Components

High margin specifications

Protection and isolation of components

Fine tuned turn on procedure

Electrical noise resistance

Components are accessible for updates, testing, and research

## Manufacturing

- Perf board hand soldering

- PCB fabrication\*

- Stand dismantle

- Stand rebuild\*

- Control systems and sensors\*

\*marks areas where challenges arose

#### Future Development

**IGBT** heatsink mounting GD PCB fabrication (gerbers provided) LV side stand configuration Field Oriented Control (FOC) Full scale integration & system testings with FOC Testings with wind turbine simulator and sensors

#### THANKS FOR LISTENING